基于FPGA的高速数字隔离型串行ADC及其工程应用之二

|

- UID

- 1023229

- 来自

- 中国

|

基于FPGA的高速数字隔离型串行ADC及其工程应用之二

3.实验结果

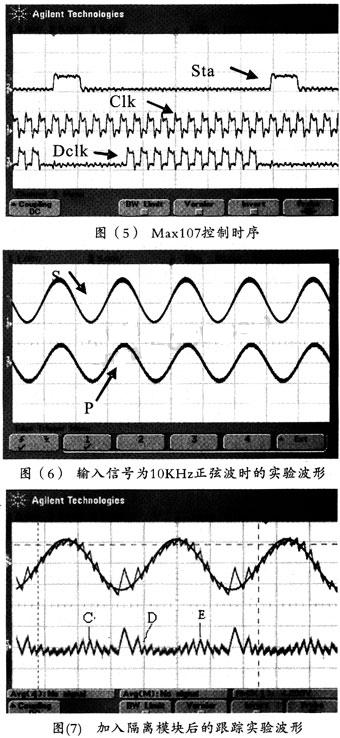

如图(5)所示,为FPGA控制Max1072的时序实验波形图参考基准电压为2.5V。图中信号Sta,Clk,Dclk分别对应图(3)中信号A,B,D。从实验结果可见Max1072的时钟频率为24MHz,启动转换信号频率为1.5MHz,与ADC时序要求完全吻合。

图(6)为隔离前后两路信号的比较情况。波形S为输入模拟信号,频率为10KHz。为调试方便外接了刷新频率为1MHz的双极型DAC。经ADC隔离采样再通过DAC将数字量转换成为模拟量即图(6)中波形P。可见数字隔离型ADC工作正常,初步验证了该方案的可行性。

图(7)为加入隔离模块后的跟踪控制原理性实验的跟踪波形。高压侧电磁干扰对控制电路的影响有很大程度地减弱。这为实现高性能的逆变单元提供了可能性。

4.结论与展望

通过实验验证了本文设计的基于高速串行模数转换器Max1072和高速隔离芯片ISO721D的数字化隔离方案的可行性。利用FPGA作为控制器初步验证了隔离模块控制时序的正确性,为跟踪型逆变单元的检测环节提供了隔离方案,有效的抑制了高压侧对控制电路的噪声窜扰。但是,由于所选DAC的性能偏低,因此没有进行更高频率信号的测试。这将在以后的工作中进一步验证和完善。 |

|

|

|

|

|