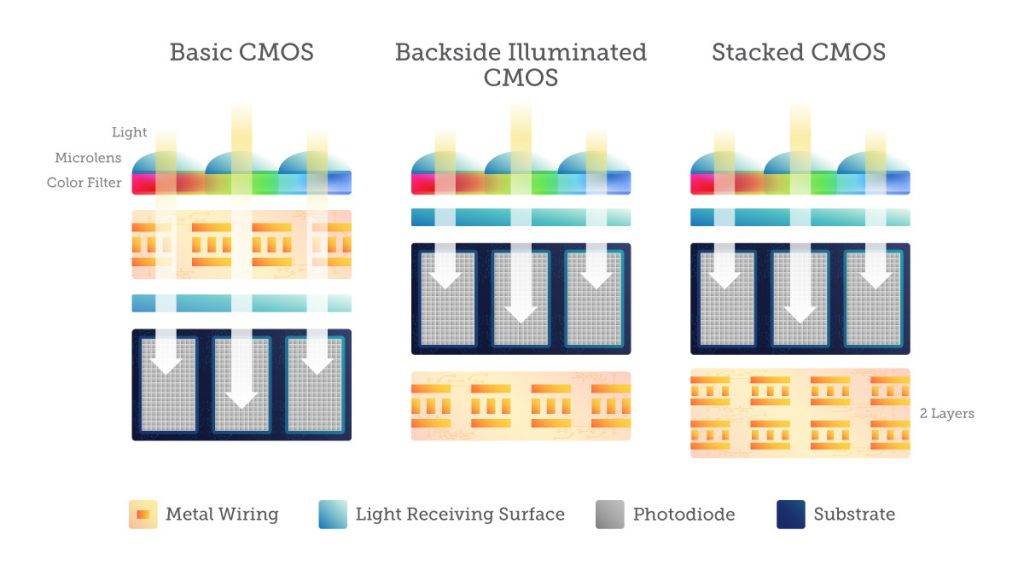

“背照式(BSI)传感器的创新颠覆了这一传统。虽然包含的元件相同,但背照式传感器将矩阵和线路置于光敏光电阴极层后面。这种设计方法在小像素设计和弱光环境中取得了更大的效益。在小像素设计中,布线更有可能占据像素空间,而在弱光环境中,可击中光敏像素的光子数量会更少。

”定制堆栈式CMOS传感器将在微型封装中增添新性能和功能

2021年12月,索尼半导体解决方案公司在IEEE国际电子器件会议上公布了一项突破性技术,推出了一项新的堆栈式CMOS图像传感器技术。传统CMOS图像传感器的光电二极管和像素晶体管分布在同一基片,而索尼的新技术将光电二极管和像素晶体管分离在不同的基片层。这种新技术有望扩大动态范围并降低噪点。

虽然这很值得注意,但这只是这项已经发展数十年技术的又一进步。如今,传感器制造商开始真正探索这种堆栈式设计方法的可能性。Yole Intelligence预测,经过2022年的过渡期后,CMOS图像传感器(CIS)市场将恢复稳定增长,2028年市场规模将达到290亿美元。该公司认为,面向更小众、销量较低的差异化市场的定制CIS产品是推动整个市场发展的关键因素。堆栈式CMOS设计为针对特定应用而设计的CMOS芯片带来了更多机会,并建立新的竞争优势。

Teledyne Imaging Machine Vision Sensors执行副总裁兼总经理Rafael Romay-Juarez解释道:

“20年前基本还属于试验性质的制造工艺,如今已经可以实现商业应用了。这仅仅是更具变革性机遇的开始,三维堆栈式传感器有机会通过具有成本效益的方式为CMOS图像传感器带来更多增值功能。”

很难想象有行业不会受到影响。2023年,成像技术的应用无处不在,扩展到了当今最重要的行业和许多下一代应用,其中包括高级驾驶辅助系统激光雷达、三维手势和人脸识别、服务无人机和机器人、太空导航以及生物医学成像。我们发现先进的科学应用采用了成像技术,这些应用包括聚变能量生成光谱学、生物医学成像、超分辨率显微镜、近红外断层扫描、鬼成像,甚至包括量子通信和密码学。CMOS成像技术的每一次进步都将帮助定义我们的未来。

那么,这种堆栈式CMOS技术是什么样的,又是如何工作的呢?

背照式传感器

背照式(BSI)传感器的创新颠覆了这一传统。虽然包含的元件相同,但背照式传感器将矩阵和线路置于光敏光电阴极层后面。这种设计方法在小像素设计和弱光环境中取得了更大的效益。在小像素设计中,布线更有可能占据像素空间,而在弱光环境中,可击中光敏像素的光子数量会更少。

BSI传感器的角度响应也更大,这为镜头设计师带来了更大的创作自由,同时传感器的读取速度可能也更快。将光转换成电信号的光电二极管和调节信号的像素晶体管相邻布置在像素芯片的同一层上。为了获得具有宽动态范围的高图像质量,必须在外形尺寸限制范围内提高饱和信号电平。

这项创新带来了新问题,即相邻像素之间的串扰会导致噪点、暗电流和混色。背面变薄的晶圆更加脆弱。即使这些问题可以通过改进生产工艺加以解决,但这样做会降低产量,增加成本。尽管存在这些缺点,但早期的BSI传感器仍被用于一些弱光性能要求极高的专门应用中。早期的用途包括工业传感器、安全摄像头、显微镜摄像头和天文系统。

而这仅仅是个开始。尽管BSI成像技术具有独特的成像优势,但它也对芯片架构产生了深远影响。如今有了BSI技术,芯片设计师可以跳出单基片的思维模式。堆栈式CMOS图像传感器的背照式像素成像芯片分布在一层(或多层)处理芯片之上,可进行更加垂直的结构设计。现在光敏层置于上面了,那它下面还能放些什么呢?还能添加哪些额外功能呢?

颠覆芯片设计:从背照式到堆栈式

随着时间的推移,设计师不断在传统CMOS芯片上添加更多功能,以提高成像传感器的性能和多功能性――时序产生、功率偏置、ADC和控制功能等等。在某些情况下,包括成像器必须每秒捕捉数百甚至数千张图像并将其数字化的情况,这意味着像素阵列甚至都不是特定裸片上的主要部分!

由于传统设计要求所有裸片都在同一基片上,因此导致了芯片设计上的一些妥协。为了获得与新增功能相同的成像性能,您可能需要在成像系统中使用更大、更难制造、更耗电的芯片。或者您需要减小芯片中图像传感器的尺寸,但这种方式可能会影响性能。

工程师们立即意识到,这种堆栈式设计可以制造出具有类似功能的小型器件,并降低制造成本。传感器设计师可将检测和处理分离到各自的层上,从而独立优化检测和成像处理。他们可以在像素层下方添加电路,以实现更低的偏移,甚至在大型成像芯片上也可以这样设计。

同样显而易见的是,三维堆栈式传感器可以为CMOS图像传感器带来更多的功能,并保持成本效益,这是单基片布局永远无法做到的。这样就有可能为更多特定应用和行业设计芯片系列,为客户提供最大限度的差异化服务。

堆栈式设计带来更快的处理速度

堆栈式传感器性能的首批实例之一出现在专业相机领域,像素层下堆栈设计的整体存储器、信号处理电路和图像处理引擎,使全画幅相机的帧频和读出速度达到了前所未有的水平。

这仅仅是个开始。几乎所有行业都能从更快的相机中受益。在极端情况下,高速成像是研究微机械、爆炸物、等离子体形成和激光剥蚀等现象的关键技术。通常,高连拍成像器采用CCD传感器,这种传感器的功率要求非常高,而且受到像素内存储器的限制,只能拍摄100帧。CMOS解决方案有优势,例如可以嵌入ADC或压缩传感等功能。传统的CMOS传感器也很难实现这种连拍性能,像素填充率低,可扩展性有限,帧捕获量通常只有几十帧。

2018年,格勒诺布尔大学的研究人员将三维堆栈式传感器设计用于解决这一问题中,创造出了一种CMOS连拍成像传感器,能够以每秒500万帧的速度捕捉数据。为此,他们在成像器下方的底层增加了内存,一次可捕捉数百张图像,他们的研究为可捕捉数千张图像的基于RAM的解决方案指明了方向!

片上神经网络?

在CMOS成像器上添加新功能,改变了传感器的功能,因此,它不仅仅是一个捕捉图像的器件。有望在芯片中实现从降噪到完整图像处理算法等各种智能功能。这能够为诸如三维和飞时测距成像、事件驱动型传感、增强现实,甚至人工智能等真正需要它的应用提供更紧凑、更省电的芯片。

与像素直接相连的大型计算单元阵列可为片上卷积神经网络和深度学习引擎铺平道路。在这一领域,能耗是一个亟待解决的问题,而将计算转移到芯片,本身也有好处。首先,像素数据可以在更靠近数据生成地的地方进行处理,从而减少数据传输能耗。数据传输能耗会占据总体能耗的很大部分。其次,源于模拟数据的像素数据也可以加以处理,从而跳过外部数据处理所需的高能耗模数转换过程,这种转换通常会占据大部分传统硬件开销以及下游计算和内存能耗。

这种想法一点也不新鲜。三十年前,塞维利亚大学的一组研究人员(该小组后来成为Teledyne Imaging机器视觉传感器团队的一部分)积极设计CMOS视觉传感器(CVIS),其中每个光电二极管周围都有一百个晶体管。这些技术实现了存储和时空滤波(卷积掩码、扩散处理等),从而能够在像素阵列基片上提取边缘、角落或兴趣点、斑点或兴趣区域、脊等特征。当时,由于缺乏堆栈式传感器技术,只能通过大像素间距来实现,从而导致设备分辨率较低。然而,情况如今发生了翻天覆地的变化。

研究人员仍然认为传感器处理器这一概念是“一个令人兴奋的探索各种权衡的乐园”。他们讨论了一个能够直接执行目标检测DNN的CMOS CIS实例,从传感器传输出来的数据量仅为几个字节(对象位置和标签),而非6MB/1080p的图像。但不同的功率和性能限制变得至关重要。例如,要从片上处理中获得性能优势,您可能需要更新、更先进的工艺节点。而且,与传统芯片相比,具有多个计算单元的堆栈式芯片的功率密度会产生更多热量,从而带来热噪点,需要在下游进行进一步处理。

三维堆栈式图像传感器架构可塑造未来

这种新的芯片设计方法和成功的商业技术展示正在激发人们的极大兴趣。像素内电路和连接提供了更高的填充系数(响应性)、多个内存节点、减少运动伪影以及更高效的HDR新技术。

三维堆栈式CMOS图像传感器正在推动激光雷达、生物医学和量子技术等许多时间分辨下一代应用领域的革命,因为它们有望实现更高的填充系数和更多的单位像素功能。

过去几年的进步相当大。很明显,堆栈式CMOS才刚刚起步,面向高要求应用的定制芯片将成为多个行业竞争优势的主要来源。

分享到:

猜你喜欢