“多年以来,FPGA业界两大巨头(Altera与Xilinx)之间的竞争白热化好像从来就没有中断过。从不断地飚高制造工艺的水平,到收购具有独特IP和技术的小公司;从开拓新的封装技术,到和业界巨头搭建多核平台,FPGA两大巨头昂扬的斗志从未衰败。对此,我对两大公司的领导者和他们的团队表示深深的敬意,真心钦佩他们的矢志不移与顽强好胜。相信正是由于他们的互不相让,才让FPGA这个产业如此迅猛地发展壮大。

”多年以来,FPGA业界两大巨头(Altera与Xilinx)之间的竞争白热化好像从来就没有中断过。从不断地飚高制造工艺的水平,到收购具有独特IP和技术的小公司;从开拓新的封装技术,到和业界巨头搭建多核平台,FPGA两大巨头昂扬的斗志从未衰败。对此,我对两大公司的领导者和他们的团队表示深深的敬意,真心钦佩他们的矢志不移与顽强好胜。相信正是由于他们的互不相让,才让FPGA这个产业如此迅猛地发展壮大。

最近以来,两大巨头的竞争焦点似乎集中在了FPGA产品的架构创新上。先是Altera公司于今年6月初宣布推出其第10代FPGA和SoC产品,采用了Intel的14nm Tri-gate工艺,其产品架构也采用了全新的增强型高性能体系架构。Altera公司产品营销资深总监Patrick 表示,该架构专为第10代产品而研发,在路由和逻辑上进行了增强,具有可扩展性,针对100万以上的逻辑单元,适合多片异构系统需求。

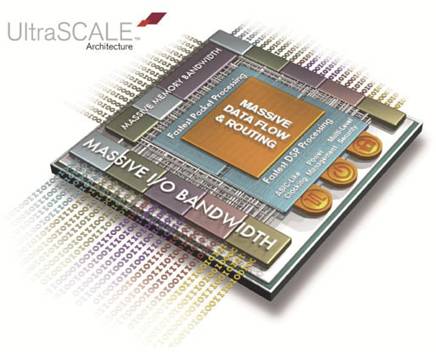

紧接着,Xilinx公司于今年7月初宣布其20nm的基于UltroScale架构的可编程器件投片,该产品被称之为业界首个ASIC级的可编程器件,也是业界首款投片的20nm半导体器件。

何为UltroScale架构?该架构是Xilinx公司为了解决目前通信业务中最大的瓶颈――互联问题而特别研发出来的崭新的产品架构。目前不断增长的海量数据流对器件带宽提出了更高要求。来自布线、时钟、关键路径和电源等各方面的智能化处理要求需要通过更创新的FPGA平台去实现。UltroScale架构在智能布线、引进ASIC特性、优化关键路径、优化电源管理和安全性上都做了大量优化。

首先,UltraScale架构的新一代互连功能与Vivado软件工具进行了协同优化,在可编程逻辑布线方面取得了真正的突破。就如同为城市繁华路段的一个十字路口精心设计成现代化高速公路或主干道,从而将交通流量从主要高速路口的一端顺畅地疏导至另一端,Xilinx为UltraScale架构加入了类似的快速通道。这些新增的快速通道可供附近的逻辑单元之间传输数据,尽管这些单元并不一定相邻,但它们仍通过特定的设计实现了逻辑上的连接。这样,UltraScale架构所能管理的数据量就会呈指数级上升。这样就从根本上完全消除了布线拥塞问题,也使器件利用率达到90%以上,且不降低性能或增加系统时延。

其次,UltroScale架构还为新的FPGA器件引入了类似ASIC的时钟,类似ASIC的多区域时钟功能使设计人员现在可以将系统级时钟放在整个晶片的任何最佳位置上,从而使系统级时钟歪斜降低多达50%。将时钟驱动的节点放在功能模块的几何中心并且平衡不同叶节点时钟单元(leaf clock cell)的时钟歪斜,这样可以打破阻碍实现多Gb系统级性能的一个最大瓶颈。该功能消除了时钟放置方面的一切限制并且能够在系统设计中实现大量独立的高性能低歪斜时钟资源,而这正是新一代设计的关键要求之一。这是与前几代可编程逻辑器件所采用的时钟方案的最大不同之处,而且实现了重大改进。

UltroScale架构还为关键路径进行了优化,从而消除了DSP和包处理的瓶颈。这些功能包括:误差校正与控制(ECC)、循环冗余校验(CRC)以及前向纠错(FEC)。增强型DSP子系统,与硬化的100 GbE MAC和Interlaken接口以及赛灵思SmartCore 包处理与流量管理IP结合在一起,采用最佳封装,能够实现线速高达数百Gbps的包处理功能。

UltroScale架构还集成了全面的电源管理功能。采用20nm的低功耗半导体工艺可降低静态功耗达35%;在逻辑架构上高效的封装与利用;更宽的DSP乘法器实现每项功能所需模块更少;采用DDR4后工作电压低于DDR3;在时钟方面为精细或粗糙时钟门控提供更多缓存;Block RAM采用动态的电源门控,硬化级联;收发器架构优化;以及通过VIVADO工具进行估算、优化和粒度控制,上述这些各个方面的优化措施综合起来,可将系统总功耗降低至Xilinx 7系列FPGA的一半。

Xilinx的安全解决方案与创新产品已经历了五代以上的发展,UltraScale All Programmable架构在这一基础上引入了多种增强型安全特性,可对载入器件内的IP提供更强的保护并实现防篡改功能。UltraScale 架构在安全性方面的改进包括:更强大更先进的AES比特流解密与认证方案;更多密钥模糊处理功能;确保在编程过程中无法对加密密钥进行外部访问。这样就能得到稳定可靠的解决方案,满足不断变化的新一代安全要求。

在谈到为何将此次推出的新产品称之为ASIC级的可编程产品,Xilinx公司全球高级副总裁亚太区执行总裁汤立人先生表示,ASIC级表明这款新的FPGA产品是一款在性能、功耗方面能够达到ASIC级别的FPGA产品,能够实现ASIC无法实现的应用。他将过去这些用ASIC无法实现的应用称之为”ASIC难民”。而这款新的FPGA平台则是为了解救这批ASIC难民而生。

两大FPGA巨头先后推出基于新的FPGA架构的产品,如此看来,架构创新将成为FPGA创新和竞争的焦点之一。产品架构的创新凝聚更多的技术力量,凝聚各层次的全面的技术研发实力,也是更大的突破。而市场的检验则是衡量孰优孰劣的最佳评判。

图1 赛灵思UltraScale架构

分享到:

猜你喜欢