“IDT 推出业界首个为便携式消费应用优化的可编程低功耗计时器件

”

IDT推出IDT VersaClock计时系列器件最新产品5P49EE801、5P49EE802、5P49EE601、5P49EE602 和 5P49EE502。VersaClock低功耗器件是一种可编程时钟生成器,专为电池供电的消费应用设计,包括智能手机、个人导航设备、MP3 播放器、摄像机和其他手持应用,以降低功耗和优化电路板布局。

新的计时器件可显著降低功耗,满足消费电子设备不断增长的功率效率需求。VersaClock 低功耗器件通过将一个时钟输出的功率需求从 30-40mW 减少到 4-8mW,延长目前便携式电子产品的电池寿命。VersaClock 低功耗解决方案还大大降低了省电模式(20μW)和32kHz 时钟主动睡眠模式(200μW)的电力消耗,这些都是行业新的低功耗基准。VersaClock 低功耗器件已开始供货。

5P49EE×产品特性

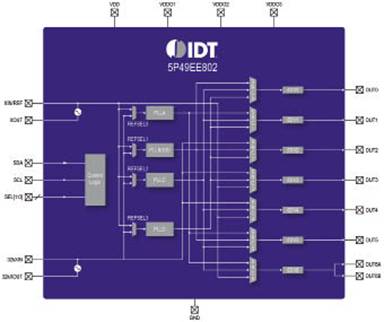

• 5个新的VersaClock低功耗器件都有4个内部锁相环,每个都可独立编程并能生成4种独有频率,有助于优化每个时钟输出的性能和提高系统精确度;

• 为了帮助设计人员提高灵活性,频率可以由时钟输入、一个温度补偿晶体振荡器(TCXO)或基本模式晶体参考生成。使用一个参考时钟允许设计人员简化设计,并在保持精确度的同时节省电路板空间;

• 4个内部锁相环中的1个支持扩频生成,以减少电磁干扰(EMI),这对满足FCC等认证要求是必需的;

• 新 VersaClock 器件可以生成 5kHz 到 120MHz 的频率,实现便携式消费应用更大的设计灵活性;

• 这些器件还兼容多种不同的输出类型――从单端 LVCMOS 到差分 VLDS,用一个器件支持不同类型的计时系统,简化设计和优化电路板布局;

• 20引脚和24引脚四方扁平无引线(QFN)封装。

详情见:www.idt.com

5P49EE802架构图

GEC

分享到:

猜你喜欢