### PMSM FOC WITH INTERLEAVED BOOST PFC ON SINGLE CHIP

NXP SE Team

PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

### AGENDA

- Introduction

- System Timing and Key Configurations

- PMSM FOC Scheme

- Interleaved Boost PFC Converter Scheme

- Test Results

- Development Tools

- Summary

- Q & A

### Introduction

#### PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

### SYSTEM FEATURES

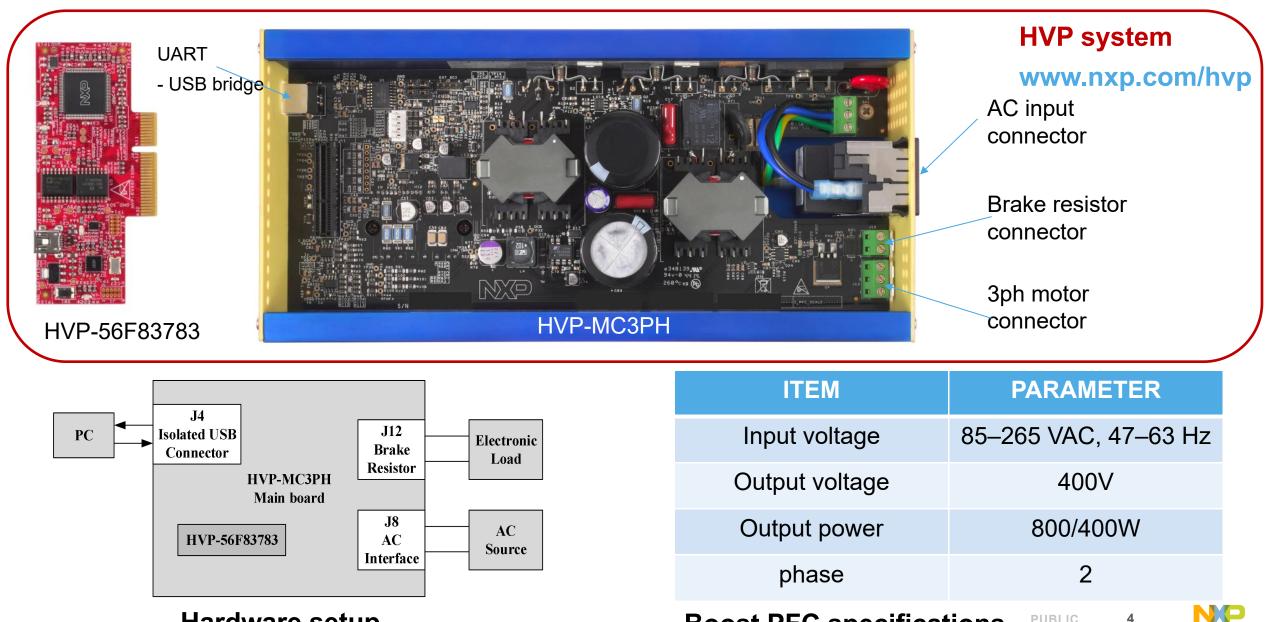

- Interleaved PFC and one PMSM control implemented on HVP-56F83783(daughter card) and HVP-MC3PH(power stage) – Single control chip solution.

- ✓ Sensorless PMSM FOC with 16 kHz PWM and control frequency

- ✓ Interleaved 2-phase boost PFC with 32 kHz control frequency and 96 kHz PWM frequency

- ✓ Remote SCI control through FreeMaster

- ✓ Software and hardware protections including OCP/OVP/UVP/OFP/UFP

- Input voltage 85–265 VAC, 47–63 Hz.

- Multiple optimization strategies to improve PF and THDI.

- Peak efficiency of the PFC stage above 96% under high line input.

- Power factor above 0.99 over a wide range of the loading.

#### HARDWARE SETUP

**Boost PFC specifications**

PUBLIC

4

Hardware setup

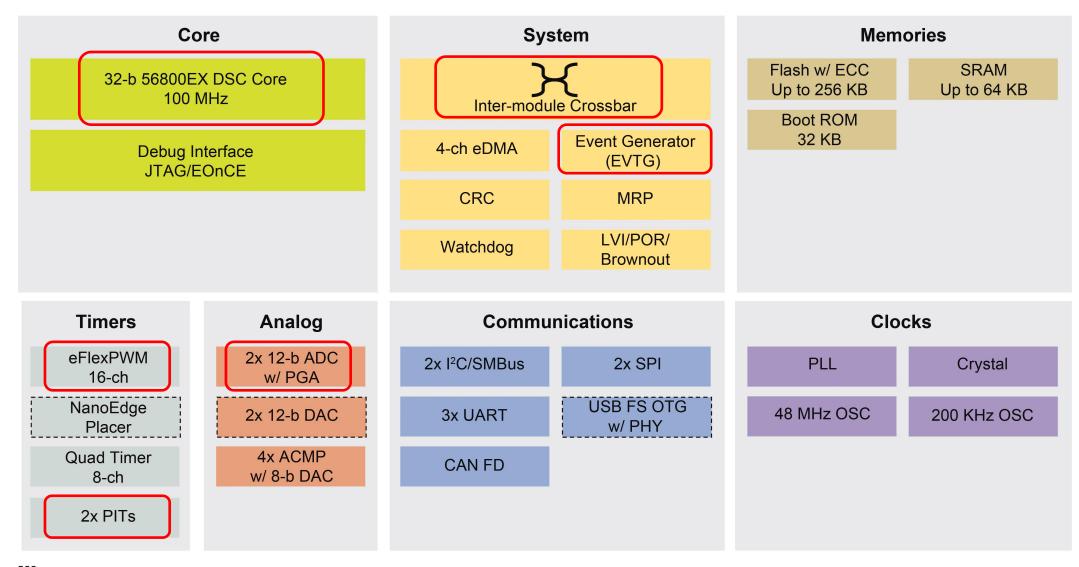

### DSC 56F83783 FEATURES

Optional

# System Timing and Key Configurations

PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

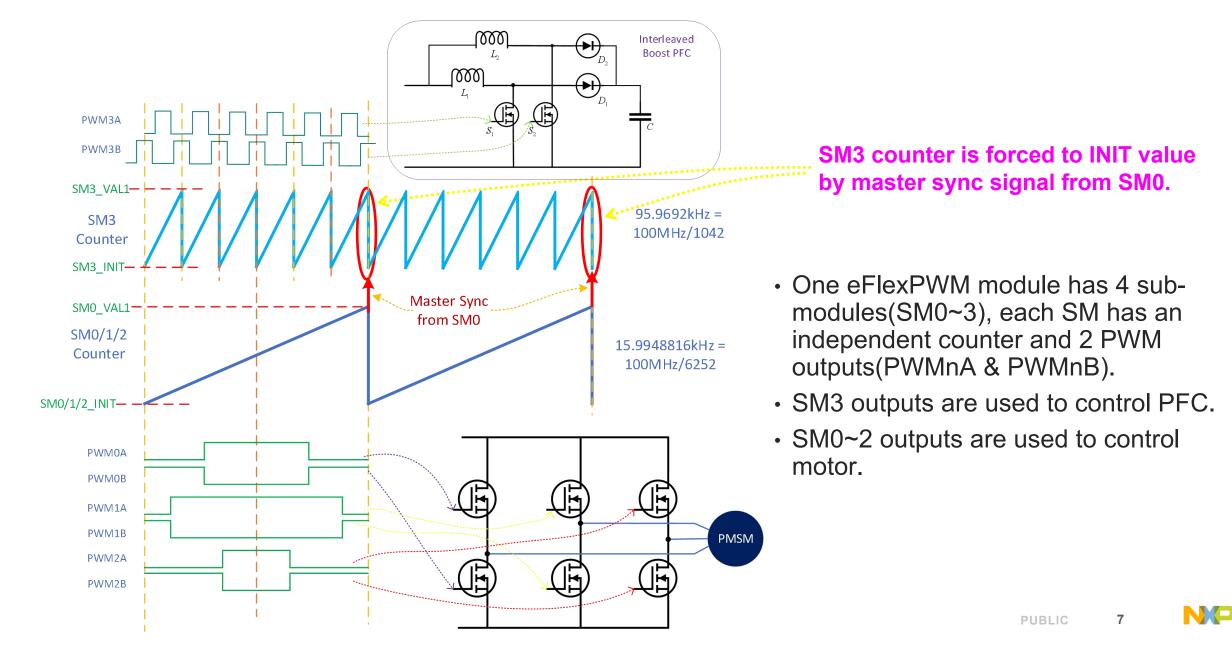

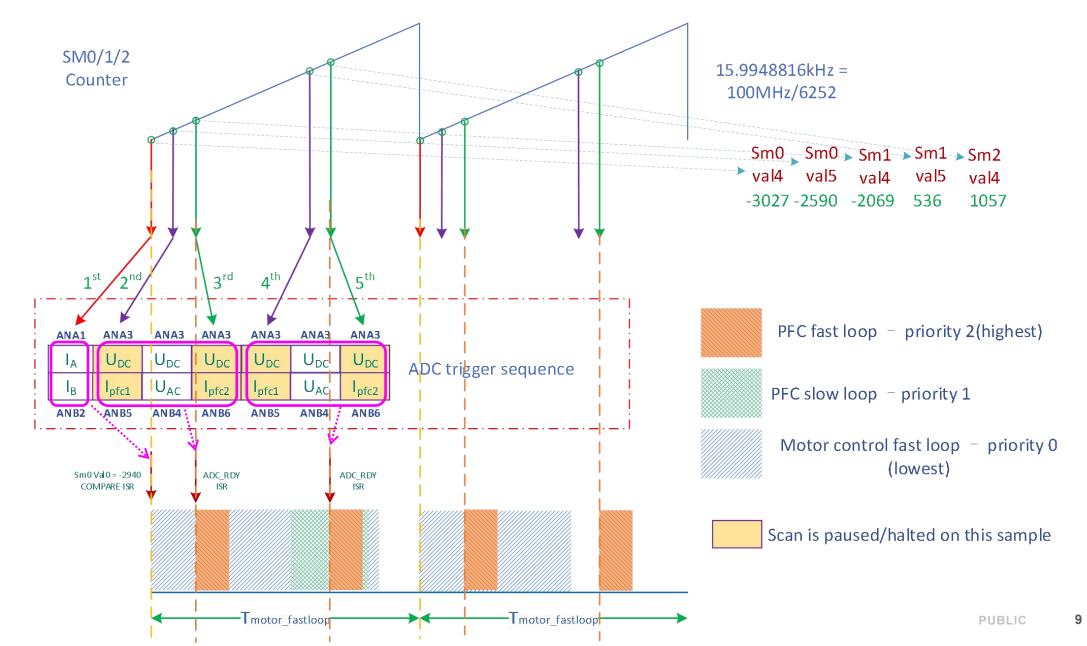

### **PWM SYNCHRONIZATION BETWEEN PFC AND MOTOR**

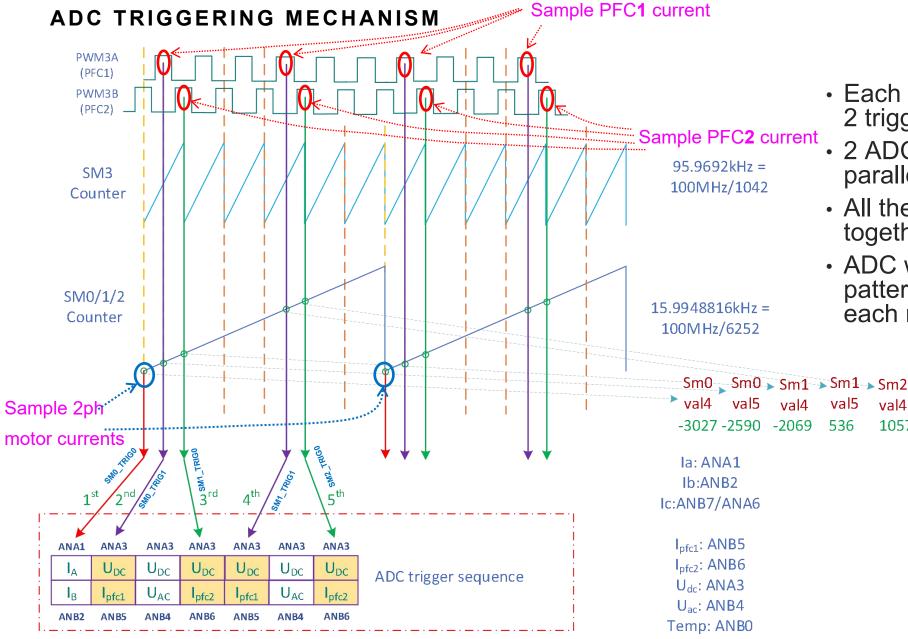

- Each SM is capable of generating 2 trigger signals.

- 2 ADC modules can work in parallel.

val4

1057

- All the trigger signals are OR'ed together to ADC.

- ADC works under a sequence pattern. This pattern is repeated in each motor control PWM period.

### MOTOR CONTROL FAST LOOP AND PFC CURRENT LOOPS ARRANGEMENT

| ltem               | Interrupt Function        | Priority             | Frequency |

|--------------------|---------------------------|----------------------|-----------|

| PFC power switch   |                           |                      | 96kHz     |

| PFC fast loop      | ADC_A_IRQHANDLER          | Priority 2 (highest) | 32kHz     |

| PFC slow loop      | PIT0_IRQHANDLER           | Priority 1           | 10kHz     |

| Motor control PWM  |                           |                      | 16kHz     |

| Motor control loop | PWMA_COMPARE_0_IRQHANDLER | Priority 0 (lowest)  | 16kHz     |

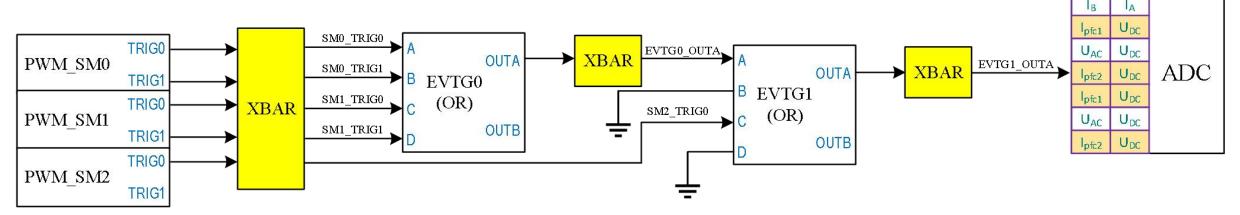

### **KEY PERIPHERALS INTERCONNECTION**

PWM triggering ADC

ADC\_TRIG = SM0\_TRIG0|SM0\_TRIG1|SM1\_TRIG0|SM1\_TRIG1|SM2\_TRIG0

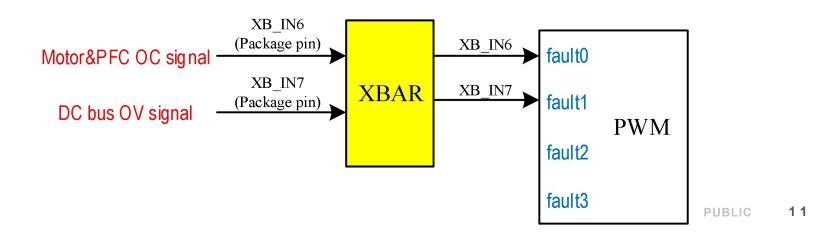

OC and OV signals disabling PWM outputs

### Hardware protection

- PFC/MOTOR current

- DC bus voltage

### Software protection

- DC bus voltage(over voltage / under voltage)

- PFC/MOTOR current

- Grid voltage (over voltage / under voltage)

- Grid frequency (over frequency / under frequency)

## **PMSM FOC Scheme**

PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

13

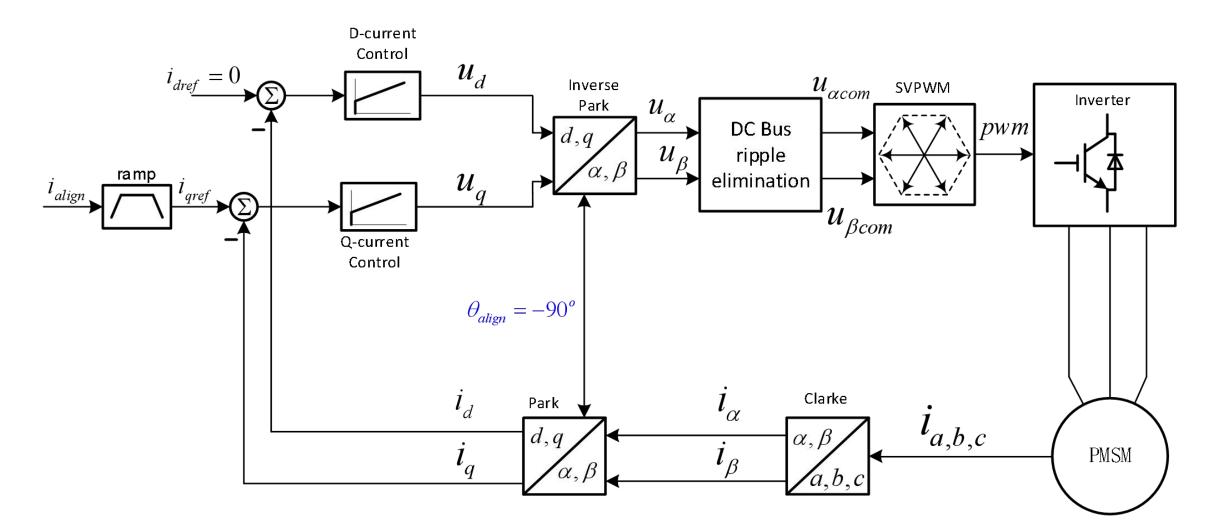

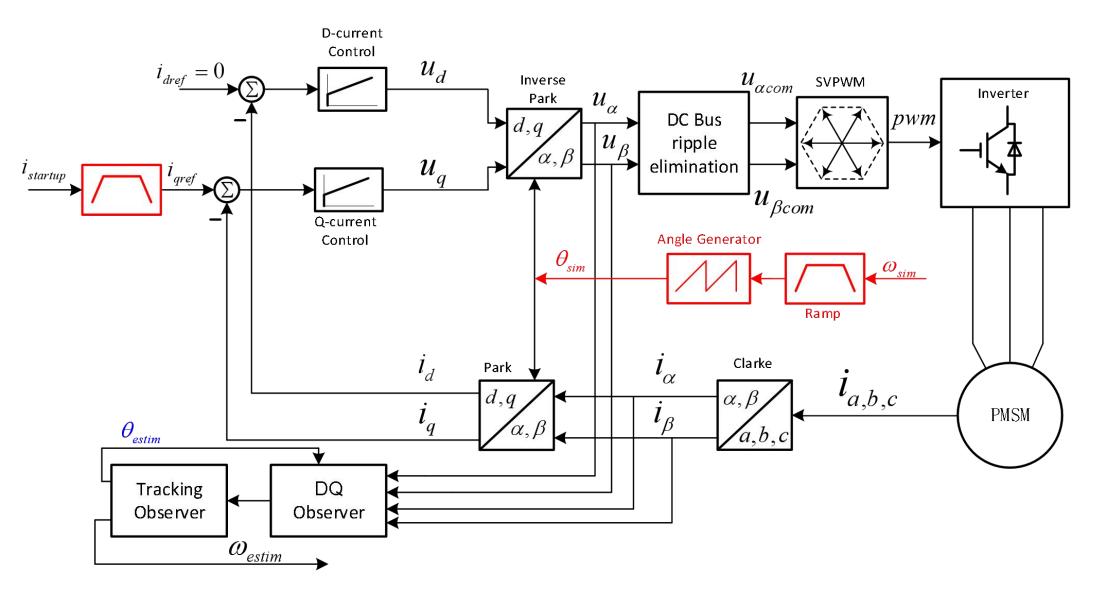

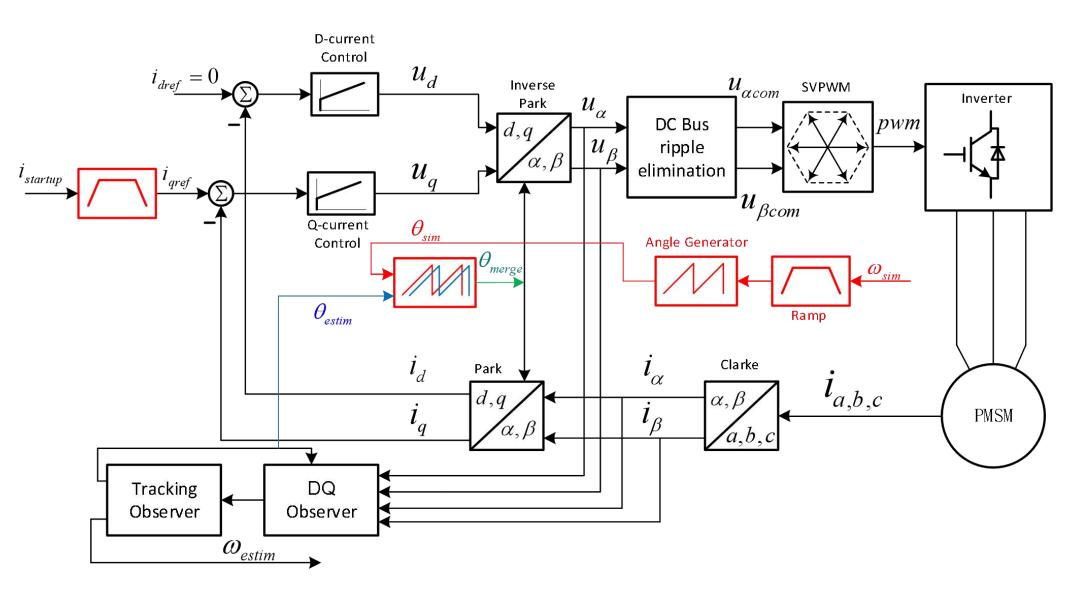

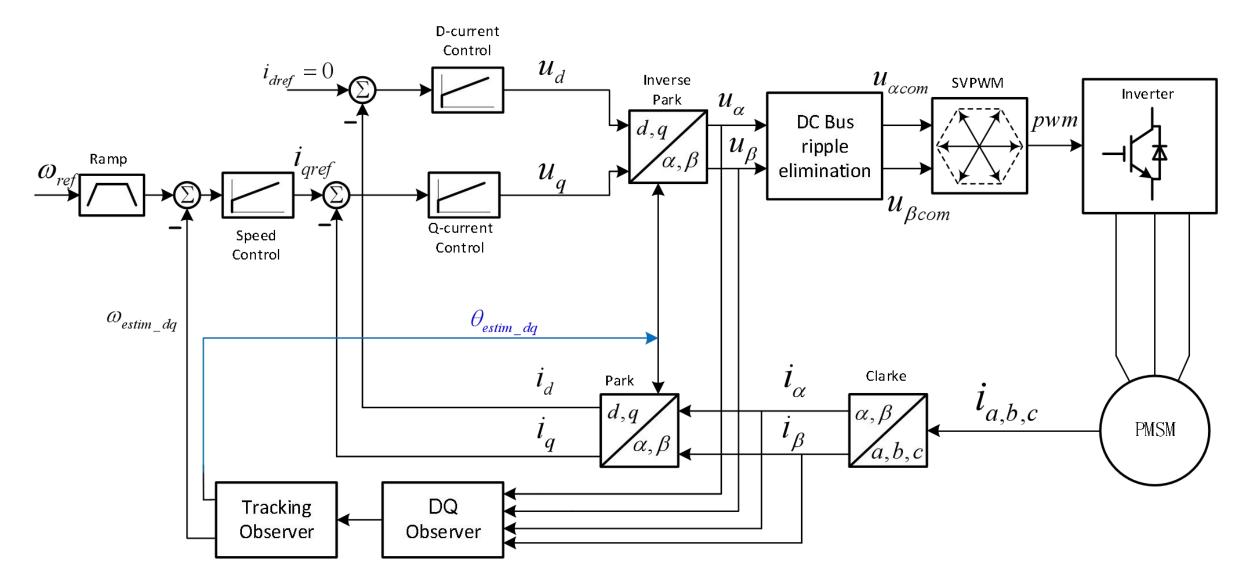

### **PMSM SENSORLESS FOC**

- It needs four major stages to run the motor:

- Alignment

- Speed open-loop startup

- Position merge

- Speed closed-loop spin

- Most FOC components and the observer are from RTCESL (Real Time Control Embedded Software Library) is used for rotor position estimation. More RTCESL information: <u>www.nxp.com/rtcesl</u>

### ALIGNMENT

### **OPEN-LOOP STARTUP**

MERGE

### **CLOSED-LOOP SPIN**

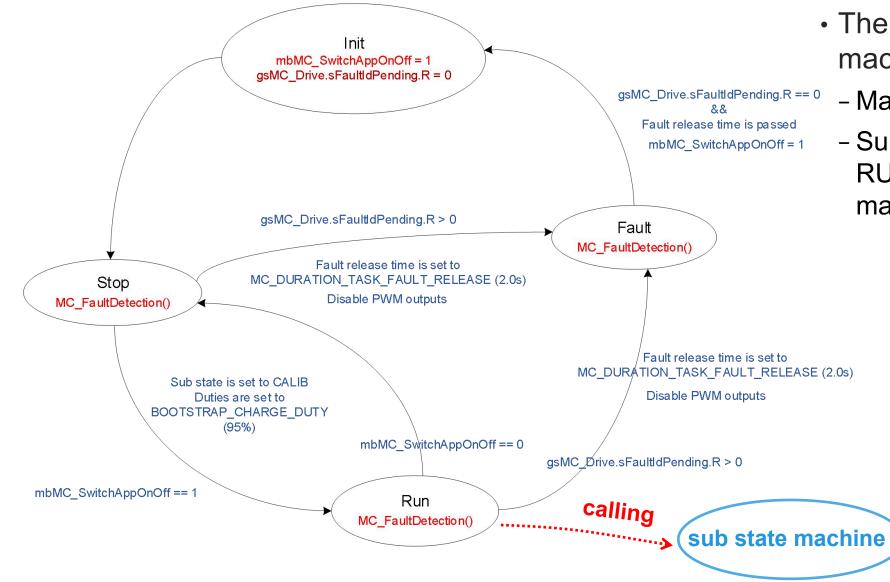

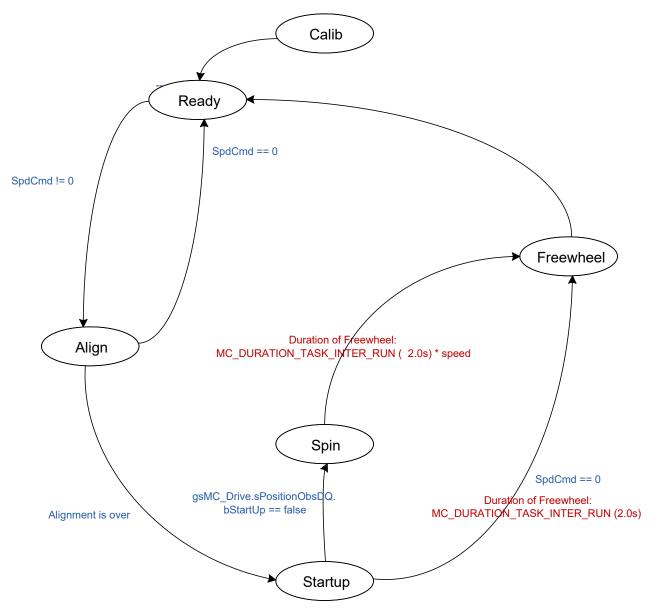

### MAIN STATE MACHINE FOR MOTOR CONTROL

- There are 2 sets of state

machines for motor control

- Main state machine

- Sub state machine residing in RUN state of the main state machine

### SUB STATE MACHINE FOR MOTOR CONTROL

PUBLIC 20

# Interleaved Boost PFC Converter Scheme

PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

2 1

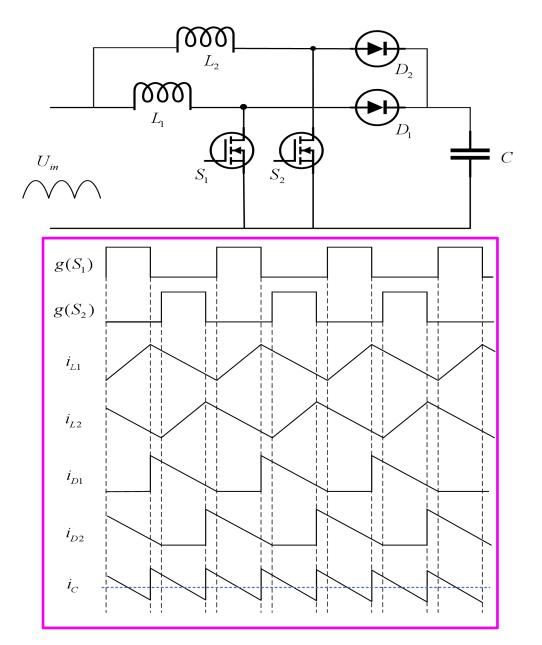

### INTERLEAVED BOOST PFC CONVERTER

- Reduce the filter size with the interleaving technology

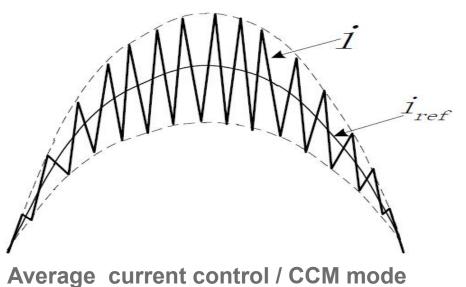

- Designed working at CCM mode for high power application

- Implemented with the average current control mode

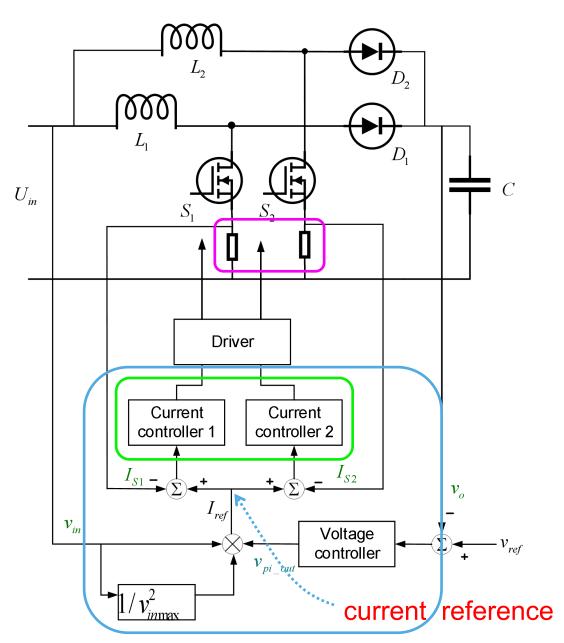

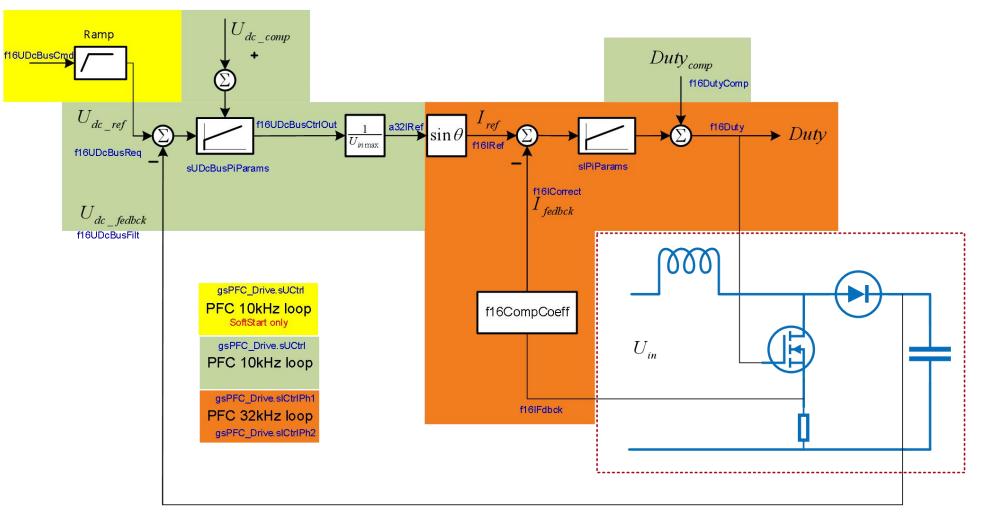

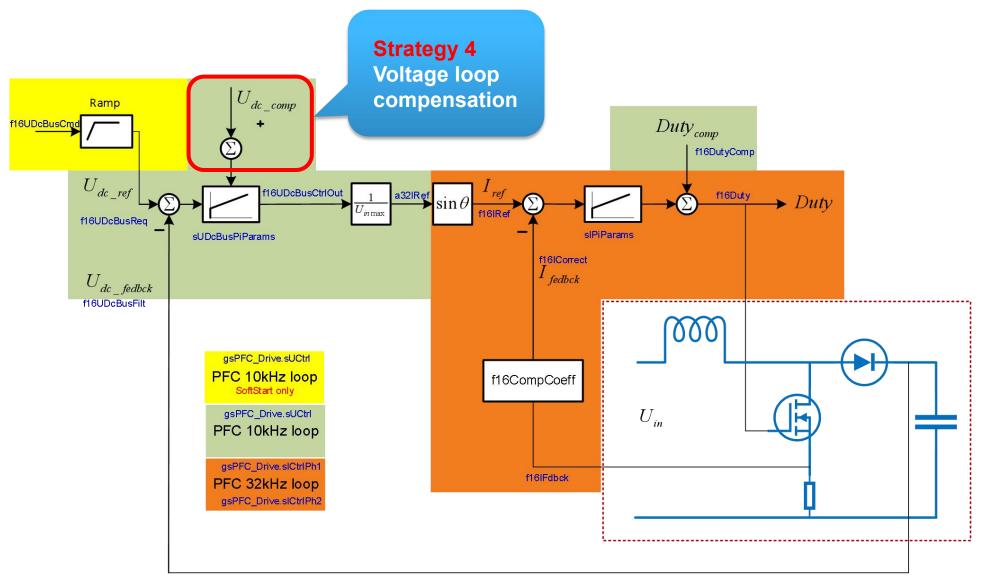

### **BASIC CONTROL STRATEGY**

- Dual loop control with the outer voltage loop and inner current loop

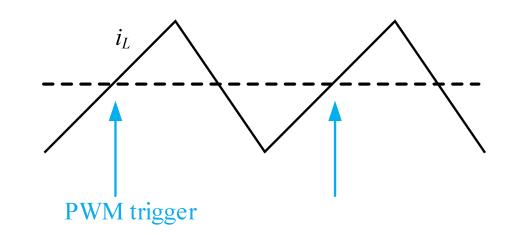

- The average current sensed by shunt resistors at the center of the switching on/off time

- Two dedicated current loops for each phase to realize the current sharing with the shared current reference

PUBLIC 23

CONTROL LOOP

### **Optimized control strategies...**

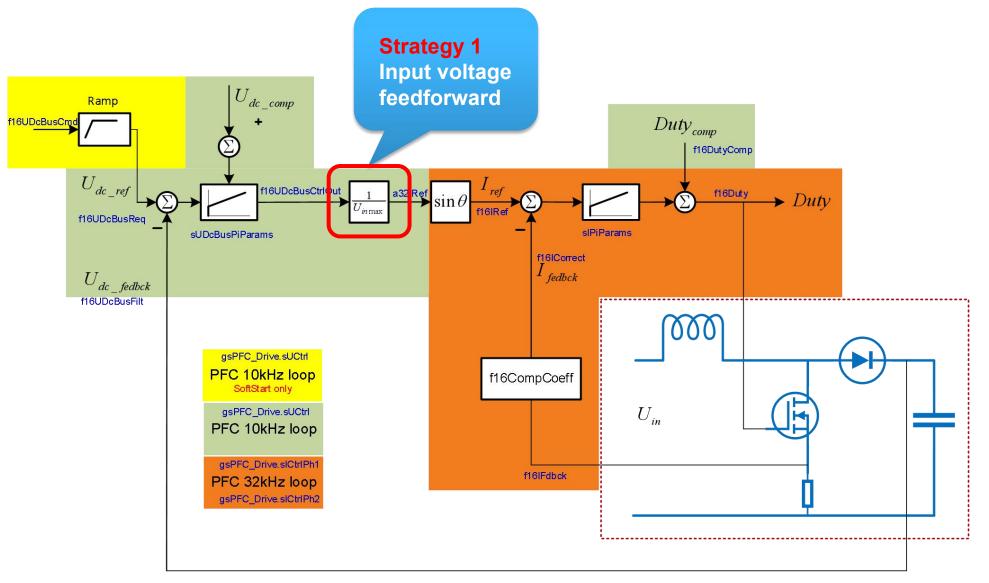

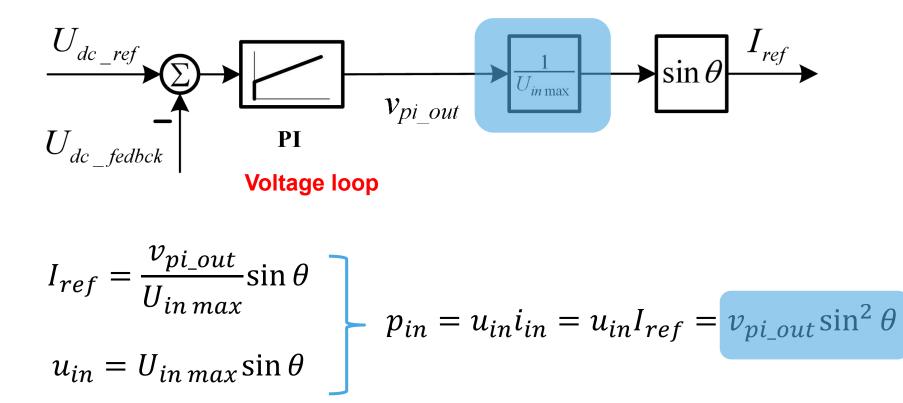

### **STRATEGY 1 : INPUT VOLTAGE FEEDFORWARD**

### **STRATEGY 1 : INPUT VOLTAGE FEEDFORWARD**

- The input power will not change with the input voltage

- Eliminate the influence of the grid voltage fluctuation

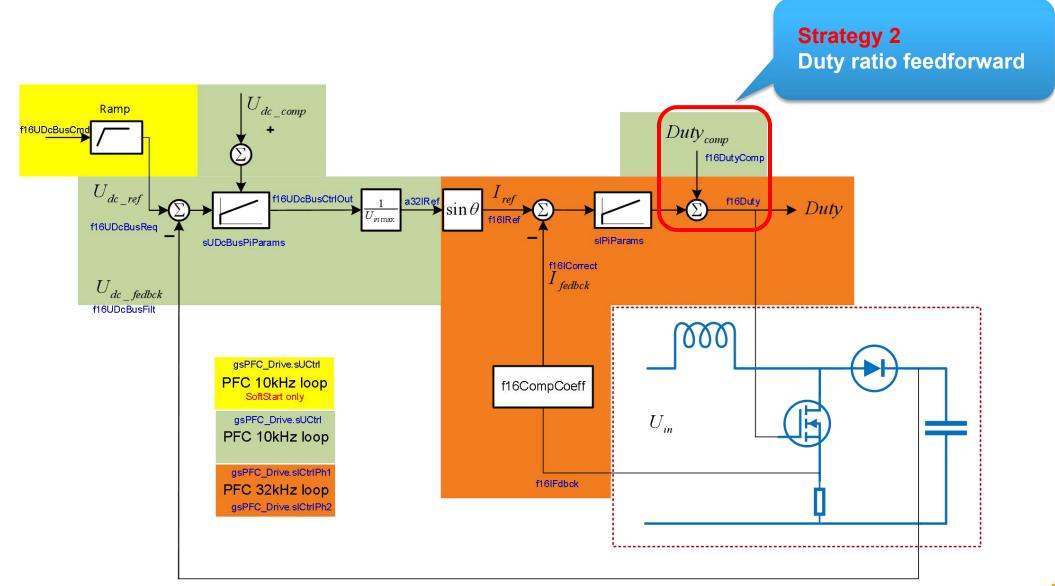

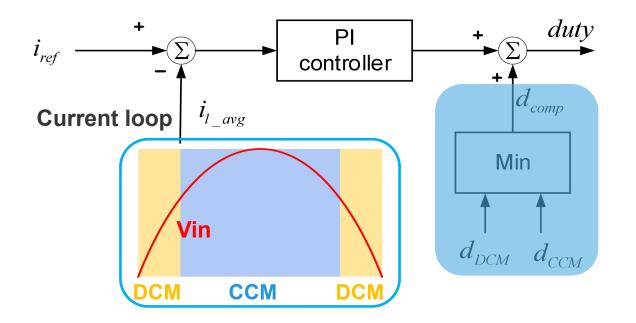

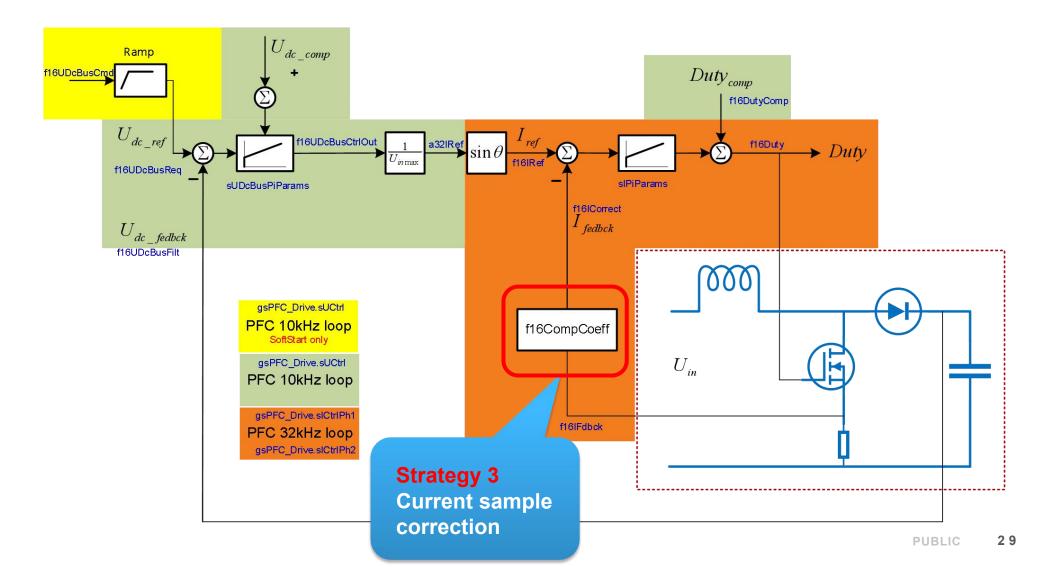

### STRATEGY 2 : DUTY RATIO FEEDFORWARD

PUBLIC 27

### STRATEGY 2 : DUTY RATIO FEEDFORWARD

- Obtain the theoretical duty based on known quantities

- Compensate the dynamics model difference between CCM and DCM mode

- Only small error need be compensated, high current loop gain isn't required

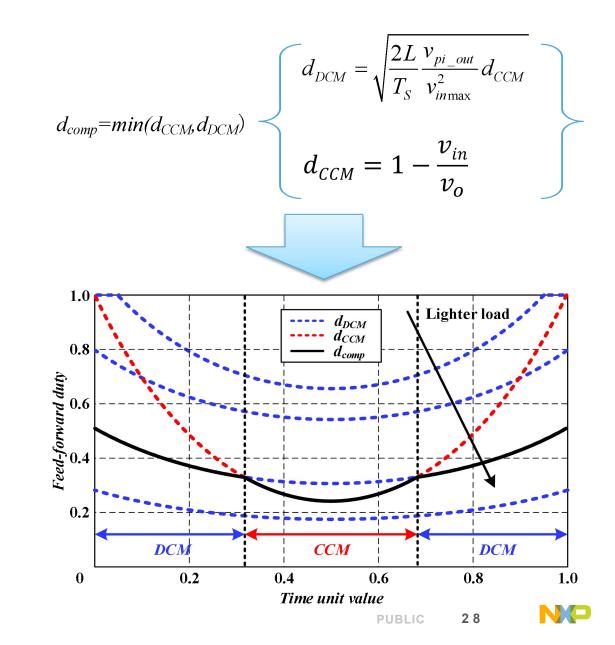

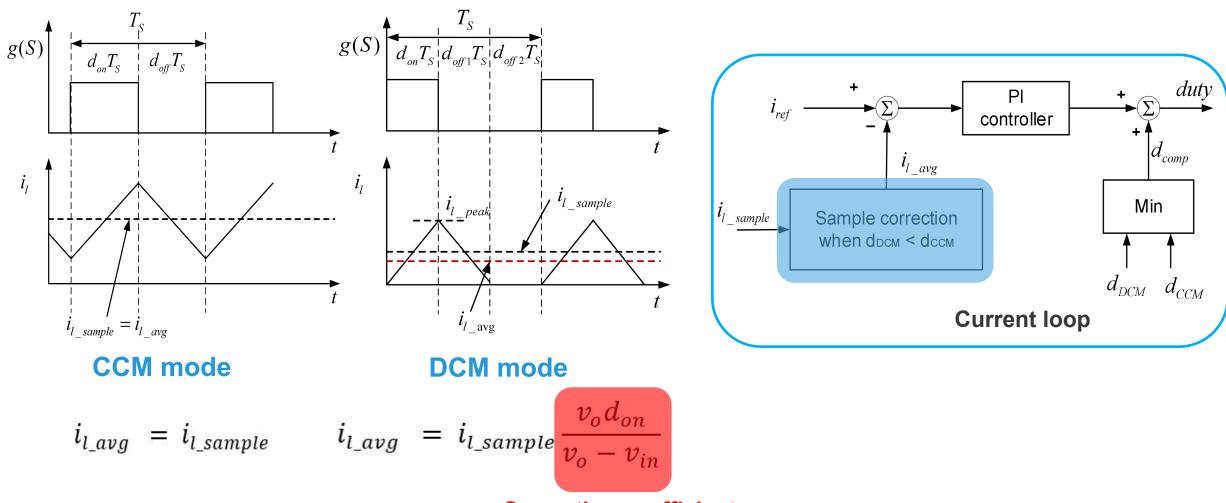

### **STRATEGY 3 : CURRENT SAMPLE CORRECTION**

### **STRATEGY 3 : CURRENT SAMPLE CORRECTION**

Correction coefficient

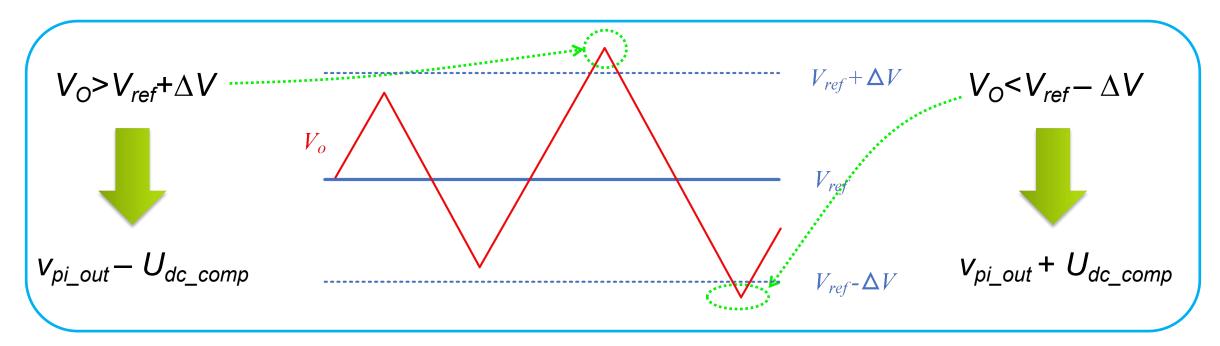

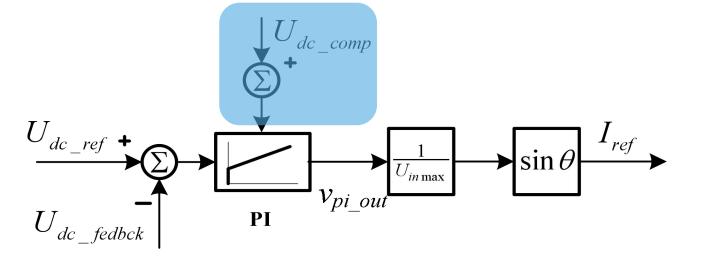

### **STRATEGY 4 : VOLTAGE LOOP COMPENSATION**

### **STRATEGY 4 : VOLTAGE LOOP COMPENSATION**

### Improve the dynamic performance of the PFC

### STRATEGY 5 : LIGHT LOAD EFFICIENCY OPTIMIZATION

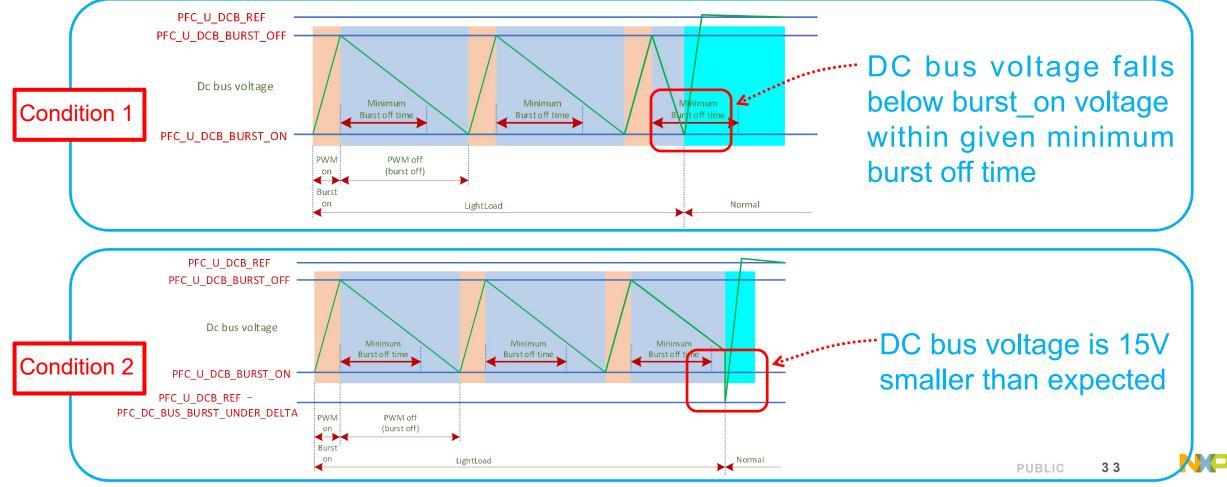

### **Burst mode**

- Block switch driving signal periodically. When switch on, the RMS value of the reference current is fixed

- Equivalent switching frequency is reduced, so the driving and switching loss is reduced

### STRATEGY 5 : LIGHT LOAD EFFICIENCY OPTIMIZATION

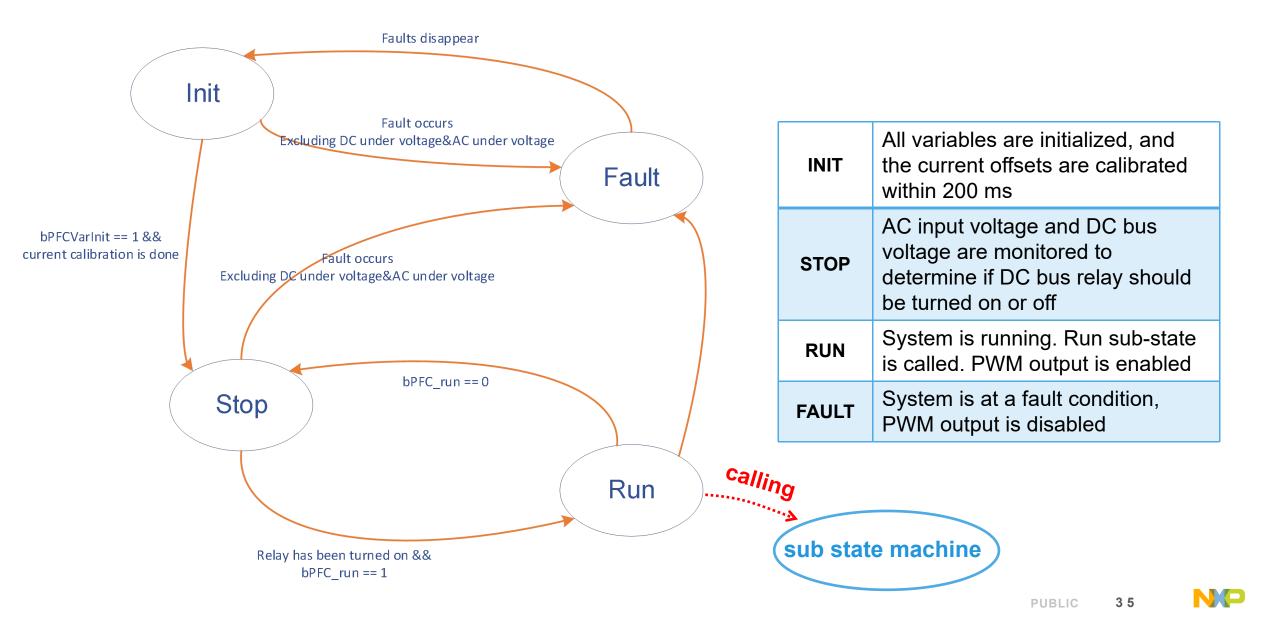

### STATE MACHINE

## **Test Results**

PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

36

#### **POWER FACTOR**

| Input AC voltage | Output power (W) | Power factor |

|------------------|------------------|--------------|

| 110V/60Hz        | 100              | 0.99         |

|                  | 200              | 0.996        |

|                  | 300              | 0.998        |

|                  | 400              | 0.998        |

| Input AC voltage | Output power (W) | Power factor |

|------------------|------------------|--------------|

| 220V/50Hz        | 200              | 0.987        |

|                  | 400              | 0.992        |

|                  | 600              | 0.997        |

|                  | 800              | 0.997        |

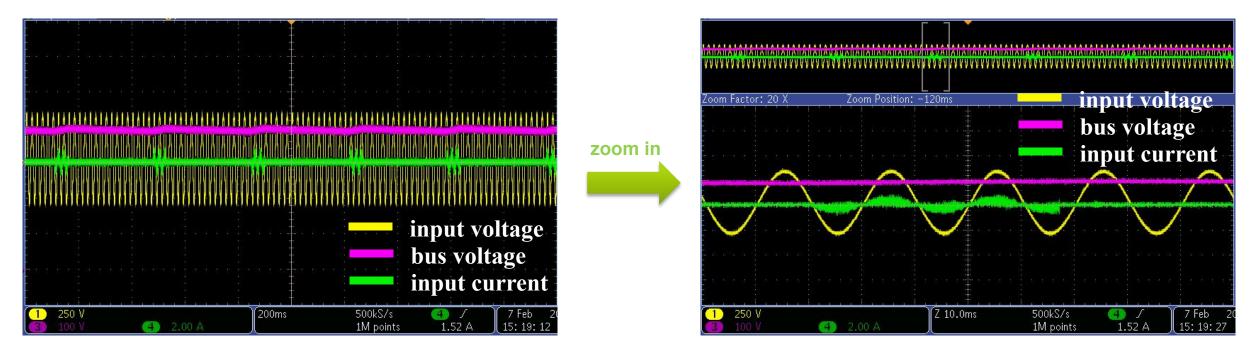

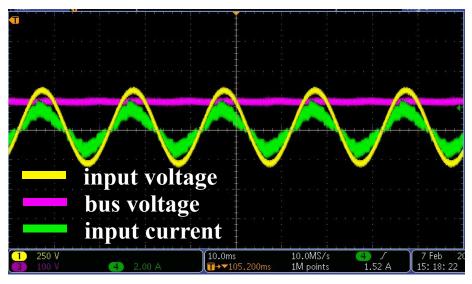

#### **NO LOAD WAVEFORMS**

Vin=220VAC/50Hz, Po=0W

**Operate at the burst mode to improve the light load efficiency**

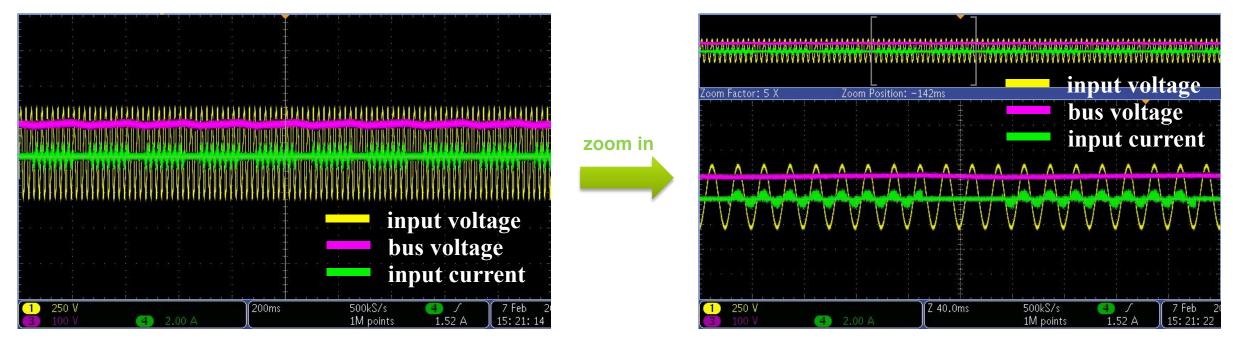

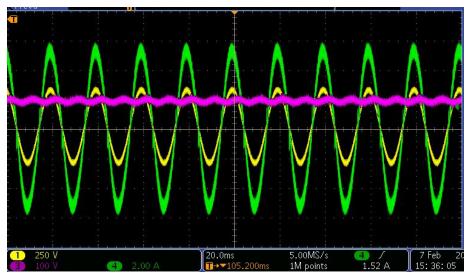

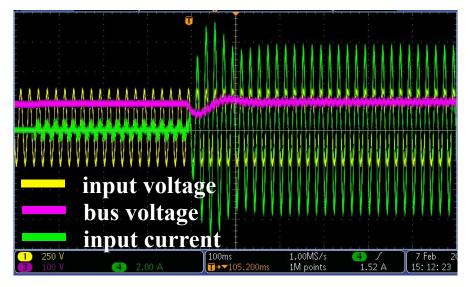

#### MOTOR LOAD WAVEFORMS

Vin=220VAC/50Hz, motor load

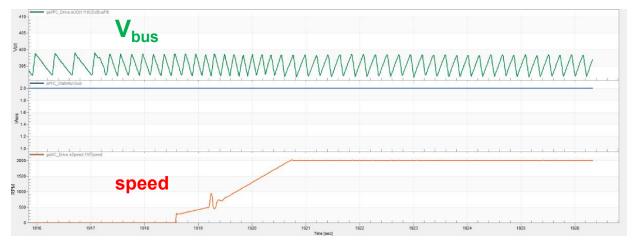

### Motor start-up waveform in FreeMaster

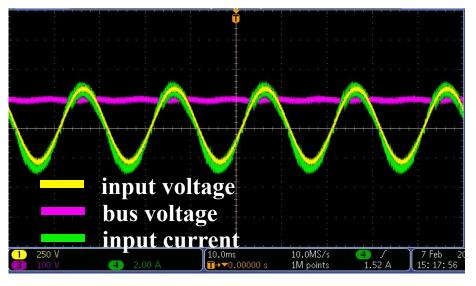

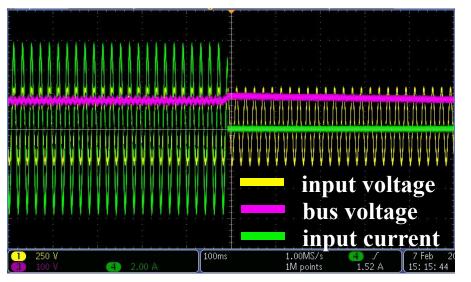

#### PFC STEADY STATE WAVEFORMS

$V_{in}$ =220VAC/50Hz,  $P_o$ =200W

V<sub>in</sub>=220VAC/50Hz, P<sub>o</sub>=400W

- The input current is a sine wave and in phase with the input voltage

- With the load increasing, the performance of the current controller becomes better

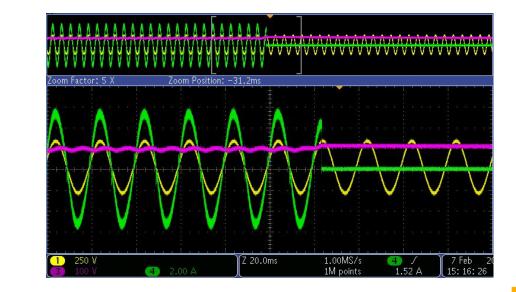

#### PFC DYNAMIC STATE WAVEFORMS

#### Vin=220VAC/50Hz, 0W to 800W load transition

- The dynamic response is fast and the voltage surge is acceptable

- The input current is in phase with the input current under the dynamic state

Vin=110VAC/60Hz, 400W to 0W load transition

zoom in

# **Development Tools**

PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

### TOOLS - ALL FREE FOR 32-BIT DSC!

- IDE <u>CodeWarrior</u> Development Studio for DSC v11.x (Compiler optimization ongoing!)

- License Free!

- Eclipse Front End for industry standard interface

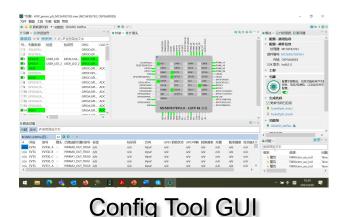

- Config GUI MCUXpresso <u>Config Tool</u> Pins, Clocks, Peripherals

- Includes pins, clocks and peripheral tools to speed up the development

- MCUXpresso <u>SDK</u>

- A comprehensive software enablement package designed to simplify and accelerate application development

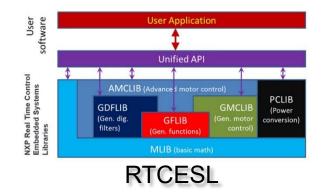

- Library <u>RTCESL</u> (Real Time Control Embedded Software Library)

- For motor control and power conversion common APIs

- Include Math / General Function / General Motor Control / General Digital Filter / Advanced Motor Control / Power Control library

- Run-time Debugging Tool <u>FreeMASTER</u>

- Non-intrusive monitoring of variables on a running system

- Oscilloscope-like display

43

PUBLIC

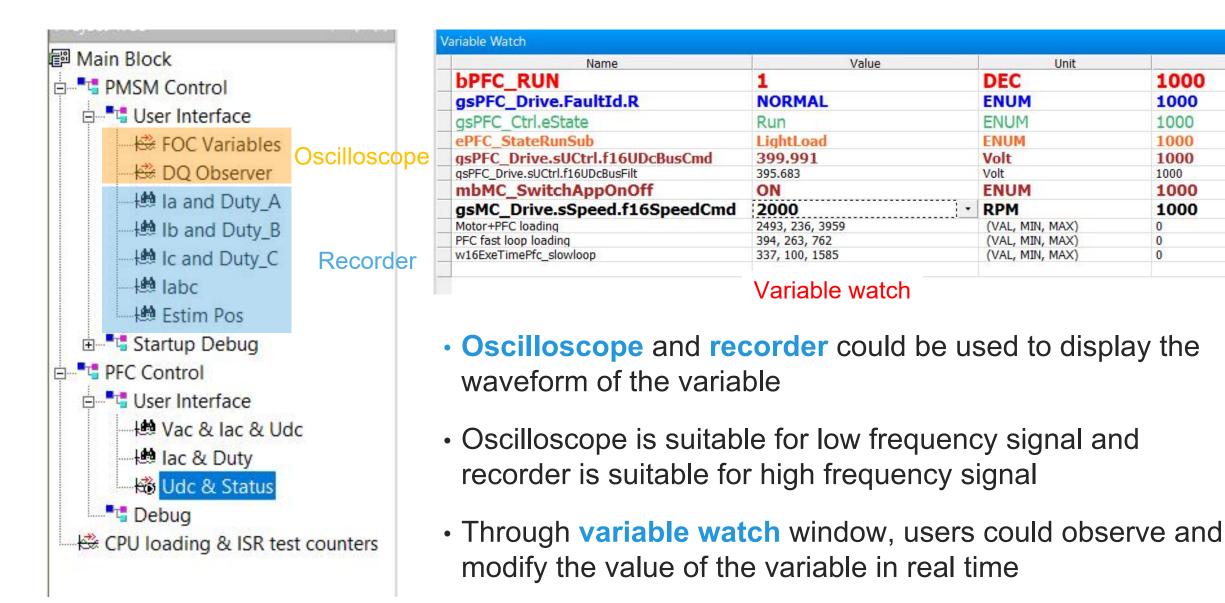

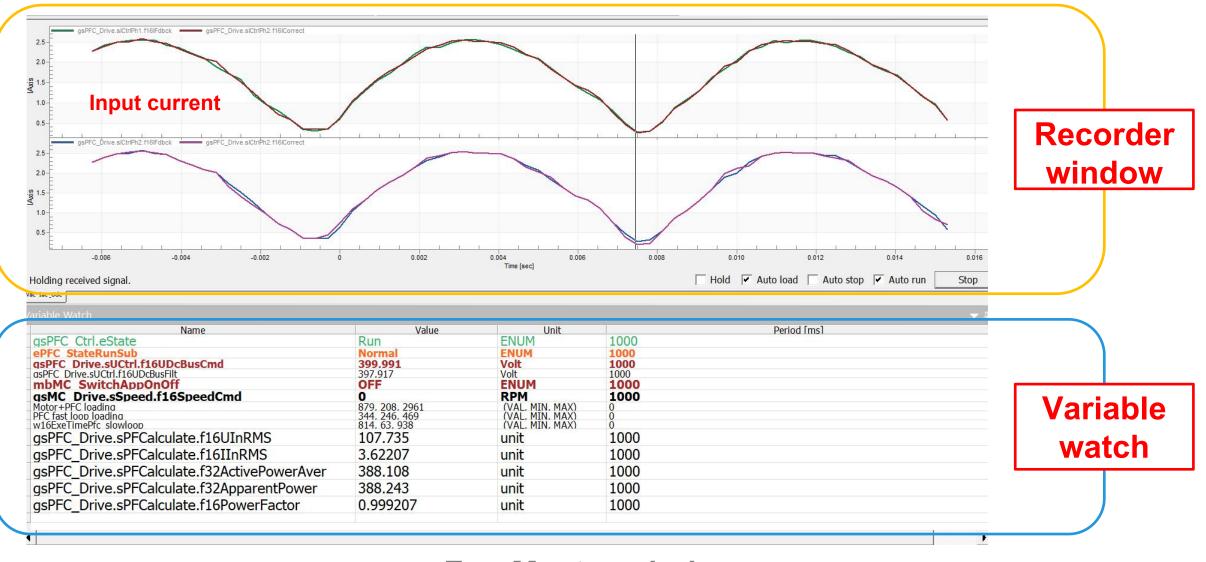

#### FREEMASTER USAGE

#### FREEMASTER USAGE

**FreeMaster window**

- The digital control of the PMSM FOC and the interleaved Boost PFC converter can be realized with one DSC chip to reduce the volume and cost of the system.

- The complex control timing is implemented with the flexible DSC peripherals.

- High light-load efficiency and low THDI is ensured by the optimized digital algorithm.

- The development cycle of the customers can be reduced by the powerful DSC enablement.

### Visit <u>www.nxp.com</u> for more information

# Q&A

## **TECHNOLOGY SHOWROOM**

#### JOURNEYS BY DESIRED ENGAGEMENT

Self-guided tour Live-streaming at set times Guided tours 60+ VIRTUAL DEMOS Focus on system solutions Set up along NXP verticals

#### JOURNEYS BY DESIRED FOCUS

Low Power Innovations Advanced Analog Connectivity Edge & Al/ML

Safety & Security

## SECURE CONNECTIONS FOR A SMARTER WORLD

SHOWROOM.NXP.COM

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.